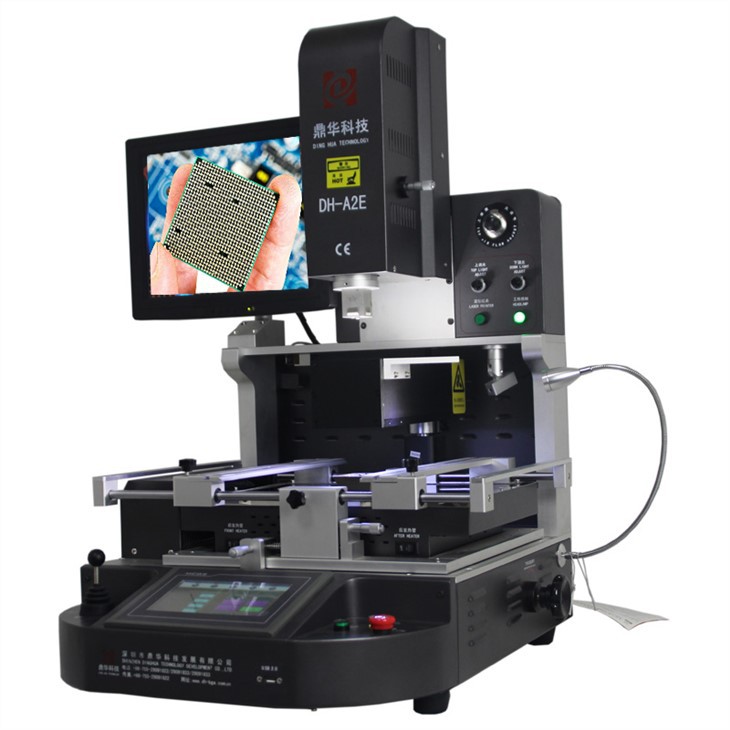

Auto Optical BGA Rework Station

Udbredt i chip-niveau reparation af bundkort på mobil, bærbar computer, computer, TV, klimaanlæg osv. Det har en høj succesrate for reparation og høj grad af automatisering og sparer masser af menneskelige anstrengelser. Vi er en professionel producent af denne maskine og har denne maskine på lager.

Beskrivelse

Auto Optical BGA Rework Station

1. Anvendelse af Auto Optical BGA Rework Station

Bundkort til computer, smart telefon, bærbar computer, MacBook logikkort, digitalkamera, klimaanlæg, tv og andet elektronisk

udstyr fra medicinsk industri, kommunikationsindustri, bilindustri mv.

Velegnet til forskellige slags chips: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP, PBGA, CPGA, LED-chip.

2. Produktegenskaber ved Auto Optical BGA Rework Station

•Høj succesrate af reparationer på chipniveau. Aflodning, montering og loddeproces er automatisk.

• Præcis justering af hver loddesamling kan garanteres med optisk justering CCD-kamera.

•Nøjagtig temperaturstyring kan sikres med 3 uafhængige varmeområder. Maskinen kan indstille og gemme

1 million af temperaturprofil.

• Indbygget vakuum i monteringshovedet opsamler BGA-chip automatisk efter afsluttet aflodning.

3.Specifikation af Auto Optical BGA Rework Station

4.Detaljer om Auto Optical BGA Rework Station

CCD-kamera (præcis optisk justeringssystem); 2.HD digital skærm; 3. Mikrometer (juster vinkel på chip);

4.3 uafhængige varmelegemer (varmluft & infrarød); 5. Laserpositionering; 6. HD touch screen interface, PLC kontrol;

7. Led forlygte ; 8.Joystick kontrol .

5.Hvorfor vælge vores Auto Optical BGA Rework Station?

6. Certifikat for Auto Optical BGA Rework Station

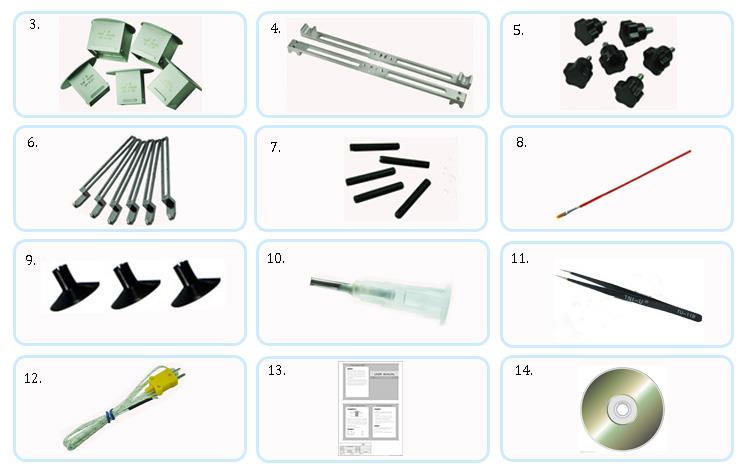

7. Pakning og forsendelse af Auto Optical BGA Rework Station

8.Ofte stillede spørgsmål

Hvordan tester man chippen?

Indledende chiptest på systemniveau

SoC er baseret på dybe submikron processer, så test af nye Soc-enheder kræver en helt ny tilgang. Fordi hver funktionel komponent

har sine egne testkrav, skal designingeniøren lave en testplan tidligt i designprocessen.

Blok-for-blok-testplanen for SoC-enheder skal implementeres: korrekt konfigurerede ATPG-værktøjer til logisk testning; korte testtider; ny højhastighed

fejlmodeller og test af flere hukommelse eller små array. For produktionslinjen finder den diagnostiske metode ikke kun fejlen, men adskiller også

defekt knude fra arbejdsknuden. Derudover bør testmultipleksteknikker anvendes, når det er muligt, for at spare testtid. Inden for højt

integreret IC-test, ATPG og IDDQ's testbare designteknikker har en kraftfuld fejladskillelsesmekanisme.

Andre faktiske parametre, der skal planlægges på forhånd, omfatter antallet af ben, der skal scannes, og mængden af hukommelse i hver pin-ende.

Grænsescanninger kan indlejres på SoC'en, men er ikke begrænset til sammenkoblingstest på tavler eller multi-chip-moduler.

Selvom chipstørrelsen er faldende, kan en chip stadig pakke millioner til 100 millioner transistorer, og antallet af testtilstande er steget til hidtil uset

niveauer, hvilket resulterer i længere testcyklusser. Dette problem kan testes. Mode komprimering for at løse, kompressionsforholdet kan nå 20 procent til 60 procent. For nutidens store skala

chipdesign, for at undgå kapacitetsproblemer er det nødvendigt at finde testsoftware, der kan køre på 64-bit-operativsystemer.

Derudover står testsoftware over for nye testproblemer forårsaget af dybe sub-mikron processer og stigende frekvens. Tidligere var ATPG-testtilstanden for

test af statiske blokeringsfejl var ikke længere relevant. Tilføjelse af funktionelle mønstre til traditionelle værktøjer gjorde det svært at finde nye fejl. En bedre tilgang er at

klassificere tidligere funktionelle tilstandsgrupper for at bestemme, hvilke fejl der ikke kan detekteres, og opret derefter en ATPG-tilstand for at fange disse manglende fejltyper.

Efterhånden som designkapaciteten øges, og testtiden pr. transistor falder, for at finde hastighedsrelaterede problemer og verificere kredsløbstidstagning, er en synkron testmetode

skal ansættes. Synkron test skal inkorporere flere fejlmodeller, inklusive transientmodeller, stiforsinkelser og IDDQ.

Nogle virksomheder i branchen mener, at kombination af blokerings-, funktionelle og forbigående/stiforsinkelsesfejl kan være den mest effektive teststrategi. For dybt

submikronchips og højfrekvent drift, transient- og vejforsinkelsestest er endnu vigtigere.

For at løse problemet med ATE-nøjagtighed ved synkronisering af testkernen og reducere omkostningerne, er det nødvendigt at finde en ny metode, der forenkler grænsefladen til

testenheden (transient- og stiforsinkelsestest kræver nøjagtigt ur ved testenhedens interface), Den sikrer, at signalet er nøjagtigt nok under testen.

Da der er stor mulighed for fabrikationsfejl i SoC-hukommelsesblokken, skal hukommelsen BIST have en diagnostisk funktion. Når et problem er fundet,

den defekte adresseenhed kan tilknyttes den redundante hukommelse på reserveadresseenheden, og den detekterede fejladresse vil blive kasseret. Undgå at kassere

hele den dyre chip.

Test af små indlejrede hukommelsesblokke eliminerer behovet for yderligere porte eller kontrollogik. For eksempel kan vektorkonverteringstestteknikker konvertere

funktionelle tilstande til en række scanningstilstande.

I modsætning til BIST-metoden kræver det funktionelle input af bypass-hukommelsesblokken ikke yderligere logik. Fordi der ikke kræves yderligere testlogik, vil SoC

udviklingsingeniører kan genbruge testmønstre, der blev dannet i fortiden.

Avancerede ATPG-værktøjer tester ikke kun makroer parallelt, men bestemmer også, om der er konflikter, samt beskriver hvilke makroer der kan testes parallelt, og hvilke

makroer kan ikke testes parallelt. Derudover kan disse makroer testes effektivt, selvom makrouret er det samme som scanningsuret (såsom synkron hukommelse).

På nuværende tidspunkt er der ikke nok testpunkter på det tætte dobbeltsidede bord, og hver kompleks chip skal være udstyret med et grænsescanningskredsløb. Uden

grænsescanninger, produktionsfejlopslag på tavleniveau er ret vanskelige og kan ikke engang findes. Med grænsescanning er test på tavleniveau ekstremt nemt

og uafhængig af det logiske kredsløb i chippen. Grænsescanning kan også konfigurere ATPG-tilstanden til chippens scanningskæde på ethvert produktionstrin.